9.15 PSPICE WINDOWS

1. Tujuan [KEMBALI]

a. Mengetahui apa itu pspice windows

b. Mengetahui rangkaian dari pspice windows

c. Mengetahui fungsi dari pspice windows

2. Alat dan Bahan [KEMBALI]

a. Baterai : berfungsi sebagai sumber energi listrik yang nanti dialirkan dalam rangkaian listrik.

b. Resistor : berfungsi sebagai penahan tegangan dan arus.

c. Transistor : berfungsi sebagai amplifier (penguat).

d. Kapasitor : berfungsi sebagai penyimpan arus atau tegangan listrik.

e. Ground : berfungsi sebagai penghantar arus listrik langsung ke bumi atau tanah saat terjadi kebocoran isolasi atau percikan api pada konsleting.

f. Osiloskop : berfungsi untuk memproyeksikan bentuk sinyal listrik agar dapat dilihat dan dipelajari.

3. Teori [KEMBALI]

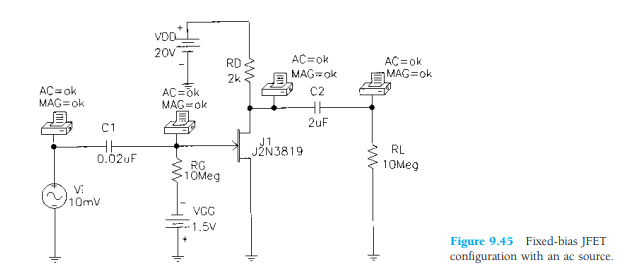

Konfigurasi Fixed-Bias JFET

Konfigurasi JFET pertama yang dianalisis menggunakan PSpice Windows adalah konfigurasi tetap-bias pada Gambar 9.45, yang memiliki JFET dengan VP 4 V dan IDSS 10 mA. 10-M resistor ditambahkan untuk bertindak sebagai jalur ke tanah untuk kapasitor tetapi pada dasarnya merupakan rangkaian terbuka sebagai beban. JFET n2 saluran J2N3819 dari perpustakaan EVAL.slb akan digunakan, dan tegangan ac akan ditentukan pada empat titik berbeda untuk perbandingan dan peninjauan.

Beta konstan ditentukan oleh :

dan dimasukkan sebagai Parameter Model menggunakan urutan Edit-Model-Edit Instance Model (Teks). Vto juga harus diubah menjadi 4 V. Elemen-elemen yang tersisa dari jaringan diatur seperti yang dijelaskan untuk transistor pada Bab 8.

Analisis jaringan akan menghasilkan cetakan Gambar 9.46. Schematics Netlist mengungkapkan node yang ditetapkan untuk setiap parameter dan menentukan node yang akan mencetak tegangan ac. Dalam hal ini, perhatikan bahwa Vi diatur pada 10 mV pada frekuensi 10kHz dari simpul 2 ke 0. Dalam daftar Junction FET MODEL PARAMETERS, VTO adalah 4 V dan BETA adalah 625E-6 seperti yang dimasukkan. SOLUSI BIAS KECIL mengungkapkan bahwa tegangan di kedua ujung RG adalah 1,5 V, menghasilkan VGS 1,5 V. Tegangan dari drain ke sumber (arde) adalah 12 V, meninggalkan penurunan 8 V di RD. ANALISIS AC pada akhir daftar mengungkapkan bahwa tegangan pada sumber (simpul 2) adalah 10 mV sebagaimana diatur, tetapi tegangan pada ujung kapasitor adalah 3 V lebih sedikit karena impedansi kapasitor pada 10 kHz — tentu saja setetes untuk diabaikan. Pilihan 0,02 F untuk frekuensi ini jelas bagus. Tegangan sebelum dan sesudah kapasitor pada sisi keluaran persis sama (ke tiga tempat), menunjukkan bahwa semakin besar kapasitor, semakin dekat karakteristik ke korsleting. Output 6,275E-2 62,75 mV mencerminkan keuntungan 6,275. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 4 mA dan gm adalah 3,125 mS. Menghitung nilai gm dari:

Konfigurasi Self-Bias JFET

Konfigurasi bias-diri pada Gambar 9.47 akan dianalisis menggunakan J2N3819 JFET dari perpustakaan dan kemudian menggunakan perkiraan rangkaian ekuivalen. Akan menarik untuk melihat apakah ada perbedaan besar dalam solusi.

Sekali lagi, VP 4 V dan IDSS 10 mA, menghasilkan Vto 4 dan Beta 6.25E-4. Analisis dijalankan dan hasil Gambar 9.48 diperoleh. Node diidentifikasi dalam Skema Netlist dan parameter dalam Junction FET MODEL PARAMETERS. SOLUSI BIAS SINYAL KECIL menunjukkan bahwa VGS 1.7114 V dan VD 14.228 V — hasil yang sangat dekat dengan solusi tulisan tangan dari 1,68 V dan 14,49 V. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 3,36 mA dibandingkan dengan tingkat yang dihitung tangan sebesar 3,3 mA dan bahwa gm adalah 2,94 mS dibandingkan dengan tingkat yang dihitung tangan sebesar 2,90 mS. AC ANALYSIS memberikan tingkat keluaran 13,3 mV pada sudut 179,9 °, yang sebanding dengan tingkat perhitungan 13,63 mV pada sudut 180 °. Hasil untuk JFET jauh lebih dekat daripada yang diperoleh untuk transistor ketika kami menggunakan elemen yang disediakan karena fitur khusus memiliki dasarnya impedansi input tak terbatas sehingga arus gerbang adalah nol ampere. Ingatlah bahwa untuk transistor, VBE adalah fungsi dari kondisi operasi.

Kami sekarang akan menyelidiki konfigurasi bias diri menggunakan model perkiraan seperti yang dilakukan untuk transistor dan melihat apakah ada peningkatan dalam hasil (dibandingkan dengan tingkat yang dihitung sendiri). Dalam hal ini, kita memerlukan sumber arus terkontrol tegangan (VCCS) yang ditemukan di perpustakaan ANALOG.slb sebagai G. Ketika dipilih, Deskripsi membaca sumber arus yang dikontrol tegangan. Ketika ditempatkan pada skema, itu akan muncul seperti yang ditunjukkan pada Gambar. 9.49. Tegangan penginderaan berada di antara tanda plus dan minus, sedangkan arus yang dikendalikan adalah antara dua terminal eksternal lainnya.

Mengklik dua kali pada simbol skematis akan menghasilkan kotak dialog PartName: G, di mana GAIN (gm) dapat diatur ke tingkat yang dihitung tangan sebesar 2,90 mS.

Hasil analisis adalah keuntungan sebesar 13,62 — hampir sama persis dengan keuntungan tulisan tangan. Pendekatan ini tentu saja valid untuk analisis ac, tetapi jika kami memeriksa SOLUSI BIAS KECIL-SINYAL, kami menemukan bahwa hasilnya tidak berarti. Oleh karena itu, padanan yang tampak pada Gambar 9.49 hanya valid untuk penguatan ac karena satu-satunya parameter yang ditentukan adalah faktor transkonduktansi ac.

Konfigurasi Pembagi Tegangan JFET

Jaringan terakhir yang dianalisis dalam presentasi Windows PSpice ini adalah konfigurasi voltagedivider pada Gambar 9.50. Perhatikan bahwa parameter yang dipilih berbeda dari yang digunakan dalam contoh sebelumnya, dengan Vi pada 24 mV dan frekuensi 5 kHz. Selain itu, level dc ditampilkan dan plot output dan voltase input akan diperoleh pada layar yang sama.

Setelah mengatur jaringan, sumber Vi harus diatur ke parameter yang ditunjukkan dengan mengklik dua kali pada sumber dan kemudian mengklik dua kali secara berurutan pada setiap parameter dan mengetikkan nilai yang benar. Masing-masing harus disimpan dan kemudian layar diubah untuk mencetak besarnya tegangan ac dan frekuensi yang diterapkan. Dalam contoh ini, parameter JFET dicetak di layar menggunakan ikon ABC. BETA tentu saja dihitung dari IDSS / VP 2. Di bawah Setup Analisis-Probe, opsi Jangan jalankan Probe otomatis, dan di bawah Pengaturan, AC Sweep dipilih dan frekuensi 5 kHz dimasukkan. Akhirnya, karena kami ingin level dc ditampilkan, opsi Tampilan Hasil pada Skema dipilih di bawah Analisis, dan Aktifkan Tampilan Tegangan diaktifkan. Level dc yang dihasilkan dari Gambar. 9.50 mengungkapkan bahwa VGS adalah 1.823 V 3.635 V 1.812 V, membandingkan dengan sangat baik dengan 1.8 V yang dihitung dalam Contoh 6.5. VD adalah 10,18 V dibandingkan dengan tingkat yang dihitung 10,24 V, dan VDS adalah 10,18 V 3,635 V 6,545 V dibandingkan dengan 6,64 V.

Untuk solusi ac, kita dapat memilih Memeriksa Keluaran dalam Analisis dan menemukan di bawah INFORMASI TITIK OPERASI bahwa gm adalah 2,22 mS, membandingkan dengan sangat baik dengan nilai yang dihitung tangan sebesar 2,2 mS, dan di bawah ANALISA AC bahwa tegangan keluaran ac adalah 125,8 mV, menghasilkan keuntungan sebesar 125,8 mV / 24 mV 5.24. Level yang dihitung sendiri adalah gmRD (2.2 mS) (2.4 k) 5.28. Bentuk gelombang ac untuk output dapat diperoleh dengan terlebih dahulu menerapkan urutan Analysis-Probe SetupAtomatis menjalankan Probe setelah simulasi. Kemudian, kembali ke Setup di bawah Analisis, dan aktifkan Transient, nonaktifkan AC Sweep, dan klik dua kali Transient untuk mendapatkan kotak dialog Transient. Untuk frekuensi 5 kHz, periode adalah 200 detik. Langkah Cetak ke 2 dtk akan memberi kami 100 titik plot untuk setiap siklus. Waktu Terakhir adalah 5 200 detik 1 ms untuk menampilkan lima siklus. The No-Print Delay adalah 0s dan Step Ceiling 2 s. Kemudian, klik ikon Jejak, pilih V (J1: d), dan bentuk gelombang keluaran dari Gambar 9.51 akan muncul. Pilih Plot-Tambah Plot-Lacak-Tambah-V (Vi: +), dan kedua bentuk gelombang akan muncul seperti yang ditunjukkan. Geser SEL ke bentuk gelombang bawah dengan hanya membawa penunjuk ke kiri dari bentuk gelombang bawah dan mengklik kiri mouse sekali. Klik ikon Toggle cursor, dan garis horizontal akan muncul di level dc dari tegangan output di 10.184 V. Klik kiri mouse dan satu set garis berpotongan akan muncul. Pilih ikon Cursor Peak, dan persimpangan akan secara otomatis pergi ke nilai puncak dari bentuk gelombang (A1 di kotak dialog). Perbedaan yang muncul di kotak dialog adalah 125,496 mV, membandingkan dengan baik dengan nilai cetak dalam file output. Perbedaannya hanya karena jumlah titik yang dipilih untuk plot; peningkatan jumlah titik plot akan membawa kedua tingkat lebih dekat.

4. Prinsip [KEMBALI]

rangkaian pspice windows merupakan rangkaian yang menghasilkan sinyal input setiap hasil dari komponen yang dihubungkan langsung pada komputer (pc). seperti rangkaian self-bias tersebut. hasil dari sinyal tersebut yang dihubunkan pada pc akan memperlihatkan atau menampilkan data - data perhitungannya

5. Rangkaian [KEMBALI]

- Rangkaian [klik disini]

- Video [klik disini]

Tidak ada komentar:

Posting Komentar